| 緯亞電子 | SMT專業貼片加工為您提供最適合的解決方案 |

公司地址:昆山市周市鎮宋家港路259號

公司電話Tel:0512-50139595

電子郵件Email: steven@pcbvia.com

1、如果設計的電路系統中包含FPGA器件,則在繪制原理圖前必需使用Quartus II軟件對管腳分配進行驗證。(FPGA中某些特殊的管腳是不能用作普通IO的)

2、4層板從上到下依次為:信號平面層、地、電源、信號平面層;6層板從上到下依次為:信號平面層、地、信號內電層、信號內電層、電源、信號平面層。6層以上板(優點是:防干擾輻射),優先選擇內電層走線,走不開選擇平面層,禁止從地或電源層走線(原因:會分割電源層,產生寄生效應)。

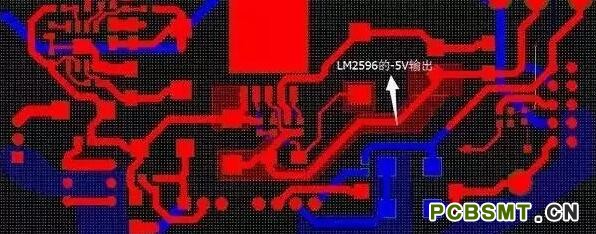

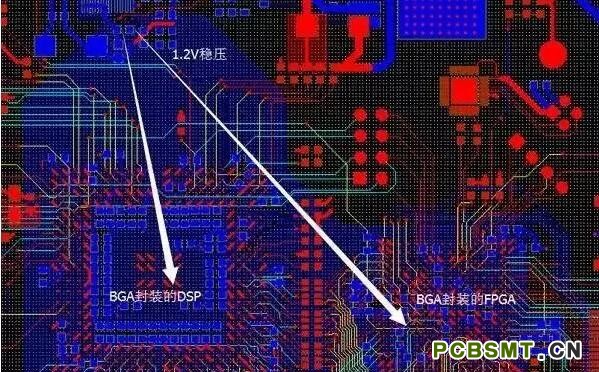

3、多電源系統的布線:如FPGA+DSP系統做6層板,一般至少會有3.3V+1.2V+1.8V+5V。3.3V一般是主電源,直接鋪電源層,通過過孔很容易布通全局電源網絡。

5V一般可能是電源輸入,只需要在一小塊區域內鋪銅。且盡量粗(你問我該多粗——能多粗就多粗,越粗越好)

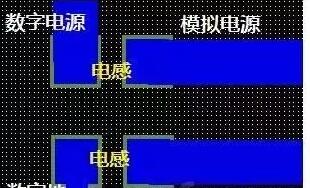

1.2V和1.8V是內核電源(如果直接采用線連的方式會在面臨BGA器件時遇到很大困難),布局時盡量將1.2V與1.8V分開,并讓1.2V或1.8V內相連的元件布局在緊湊的區域,使用銅皮的方式連接,如下圖:

總之,因為電源網絡遍布整個PCB,如果采用走線的方式會很復雜而且會繞很遠,使用鋪銅皮的方法是一種很好的選擇!

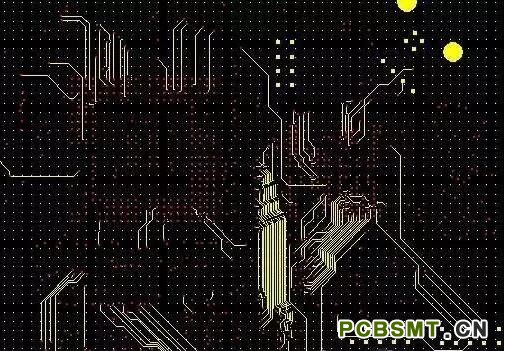

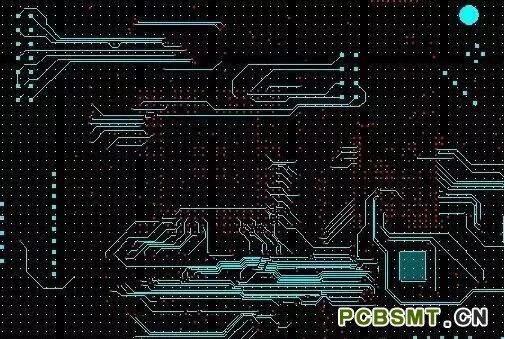

4、鄰層之間走線采用交叉方式:既可減少并行導線之間的電磁干擾(高中學的哦),又方便走線(參考資料1)。如下圖為某PCB中相鄰兩層的走線,大致是一橫一豎。

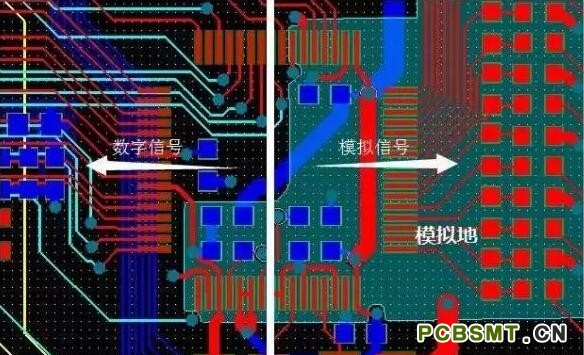

5、模擬數字要隔離,怎么個隔離法?布局時將用于模擬信號的器件與數字信號的器件分開,然后從AD芯片中間一刀切!

模擬信號鋪模擬地,模擬地/模擬電源與數字電源通過電感/磁珠單點連接。

6、基于PCB設計軟件的PCB設計也可看做是一種軟件開發過程,軟件工程注重“迭代開發”的思想,我覺得PCB設計中也可以引入該思想,減少PCB錯誤的概率。

(1) 原理圖檢查,尤其注意器件的電源和地(電源和地是系統的血脈,不能有絲毫疏忽)

(2) PCB封裝繪制(確認原理圖中的管腳是否有誤)

(3) PCB封裝尺寸逐一確認后,添加驗證標簽,添加到本次設計封裝庫

(4) 導入網表,邊布局邊調整原理圖中信號順序(布局后不能再使用OrCAD的元件自動編號功能)

(5) 手工布線(邊布邊檢查電源地網絡,前面說過:電源網絡使用鋪銅方式,所以少用走線)

總之,PCB設計中的指導思想就是邊繪制封裝布局布線邊反饋修正原理圖(從信號連接的正確性、信號走線的方便性考慮)。

7、晶振離芯片盡量近,且晶振下盡量不走線,鋪地網絡銅皮。多處使用的時鐘使用樹形時鐘樹方式布線。

8、連接器上信號的排布對布線的難易程度影響較大,因此要邊布線邊調整原理圖上的信號(但千萬不能重新對元器件編號)

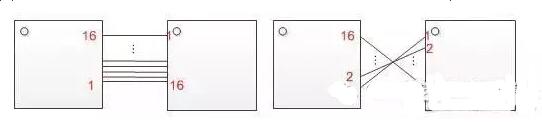

9、多板接插件的設計:

(1) 使用排線連接:上下接口一致

(2) 直插座:上下接口鏡像對稱,如下圖

10、模塊連接信號的設計:

(1) 若2個模塊放置在PCB同一面,如下:管教序號大接小小接大(鏡像連接信號)

(2) 若2個模塊放在PCB不同面,則管教序號小接小大接大

這樣做能放置信號像上面的右圖一樣交叉。當然,上面的方法不是定則,我總是說,凡事隨需而變(這個只能自己領悟),只不過在很多情況下按這種方式設計很管用罷了。

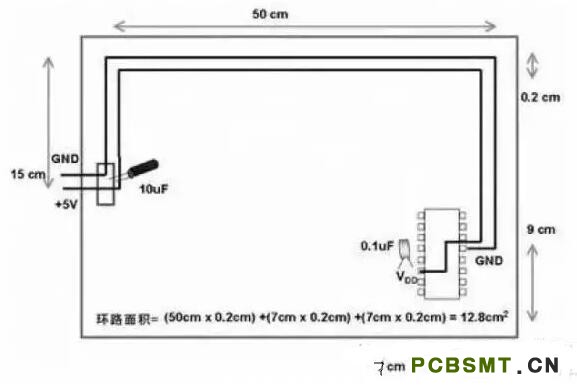

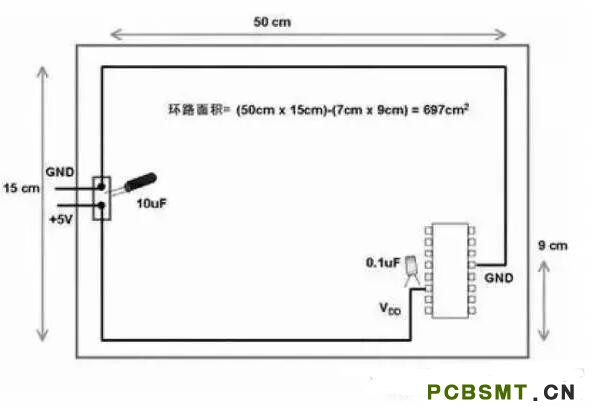

11、電源地回路的設計:

上圖的電源地回路面積大,容易受電磁干擾

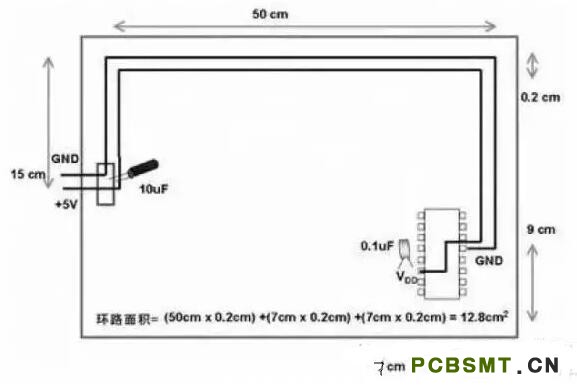

上圖通過改進——電源與地線靠近走線,減小了回路面積,降低了電磁干擾(679/12.8,約54倍)。因此,電源與地盡量應該靠近走線!而信號線之間則應該盡量避免并行走線,降低信號之間的互感效應。

本文《十一條PCB設計經驗 讓你受用一生》由昆山緯亞電子有限公司發布在分類[行業新聞],未經許可,嚴禁轉載發布。

本文《十一條PCB設計經驗 讓你受用一生》由昆山緯亞電子有限公司發布在分類[行業新聞],未經許可,嚴禁轉載發布。

上一篇:高速PCB設計中的時序分析

下一篇:如何防止別人抄你的PCB板?